Laporan Akhir 3 (Percobaan 3a)

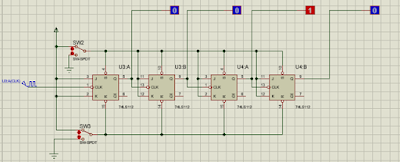

Berbagai variasi kondisi dalam percobaan 3a, sesuai dengan jurnal, adalah sebagai berikut: Jika S0=1, S1=don't care, S2=don't care, S3=don't care, maka output yang dihasilkan adalah 0000 dan logic probe tidak menyala (off). Hal ini terjadi karena pada counter IC 74192 dan IC 74193, kaki S0 terhubung ke kaki MR yang berfungsi sebagai reset, sehingga output yang terbaca adalah 0000. Jika S0=0, S1=0, S2=don't care, S3=don't care, output yang dihasilkan adalah off pada kedua counter IC 74192 dan IC 74193. Jika S0=0, S1=0, S2=0, S3=0, maka output yang dihasilkan juga adalah off. Jika S0=0, S1=clock, S2=1, S3=1, maka counter akan berada dalam kondisi counter up synchronous. Pada kondisi ini, S1 terhubung ke sinyal clock dan S2 berlogika 1, sehingga IC 74193 akan mencacah secara berurutan dari hexadesimal 0-15 (F), yaitu dari 0000-1111, dan IC 74192 akan mencacah dari 0-9. Jika S0=0, S1=1, S2=clock, S3=1, maka counter akan berada dalam kondisi counter down synchronous. Pada kondisi ini, S2 terhubung ke sinyal clock dan S1 berlogika 1, sehingga IC 74193 dan IC 74192 akan mencacah secara berurutan dari hexadesimal 15 (F)-0, yaitu dari 1111-0000.

5. Video Rangkaian [Kembali]

.png)

.png)

.png)

.png)

.png)

.png)

.png)

.jpeg)