Laporan Akhir 1 (Percobaan 1)

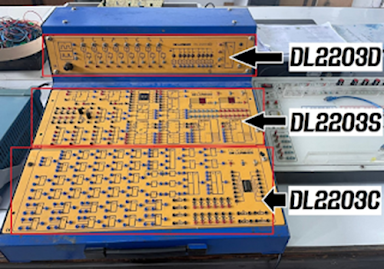

2. Alat dan Bahan

[Kembali]

Kelebihan JK Flip-flop adalah tidak adanya kondisi terlarang atau yang berarti di beri berapapun inputan asalkan terdapat clock maka akan terjadi perubahan pada keluarannya / outputnya. berikut adalah symbol dan tabel kebenaran dari JK Flip-Flop.

Prinsip kerja rangkaian di atas adalah menggunakan empat JK flip-flop yang terhubung dengan power. Dengan demikian, input pada JK flip-flop tersebut bersifat toggle. Akibatnya, output toggle pada masing-masing IC akan berubah sesuai dengan aktivitas pada clock, yaitu ketika clock aktif dalam keadaan rendah (Fall time).

Pada percobaan pertama, clock input hanya terhubung ke JK flip-flop pertama atau yang berada di sebelah kanan. Ketika clock awalnya bergerak dari 0 menuju waktu naik (rise time), maka tidak ada perubahan pada output JK flip-flop pertama, begitu pula dengan JK flip-flop berikutnya. Kemudian, saat clock berada dalam keadaan waktu rendah (fall time), JK flip-flop pertama akan berubah menjadi 1. Namun, JK flip-flop kedua tidak terpengaruh karena ia bergantung pada output JK flip-flop pertama, sehingga terjadi penundaan (delay time). Sebagai akibatnya, clock IC kedua berada dalam keadaan waktu naik (rise time), sehingga output IC kedua menjadi logika 0. Proses ini berlanjut untuk IC ketiga dan keempat, di mana mereka menerima peningkatan atau penurunan dari flip-flop sebelumnya.

5. Video Rangkaian

[Kembali]

1. Analisa output percobaan berdasarkan IC yang digunakan!

Telah dilakukan percobaan 1 yang mana didapatkan penjelasan sebagai berikut

- Rangkaian asyncronous counter menggunakan J-K flip flop.

- Inputan 1 sehingga R-S tidak aktif karena R-S aktif low.

- Hanya flip flop pertama yang terhubung secara langsung ke sinyal clock, inputan clock flip flop selanjutnya terhubung dengan output Q flip flop sebelumnya.

- Output pada H0, H1, H2, H4 bergulir dari 1 ke 0.

- Rangkaian asyncronous counter up karena clock terhubung ke output Q.

- Timing diagram 8 fasa pada jurnal.

2. Analisa sinyal output yang dikeluarkan J-K flip flop kedua dan ketiga!

- J-K flip flop ke 2 output Q nya ke H1, ketiga output Q nya ke H2.

- Clock J-K flip flop ke 2 terhubung ke output J-K flip flop 1, ketika terjadi fall time pada output H0 maka pada sinyal output H1 berubah (0 ke 1), begitu seterusnya.

- Clock J-K flip flop ke 3 terhubung ke output J-K flip flop 2, ketika terjadi fall time pada output H1 maka pada output H2 berubah (0 ke 1), output tidak berubah / sama dengan output sebelumnya.

HTML klik disini

Rangkaian klik dsini

.png)

.png)

Tidak ada komentar:

Posting Komentar